STM32的运行

STM32的运行

# 主线的运行:主线仲裁

这里讲到的总线是片外的外部总线:指令、数据与系统总线

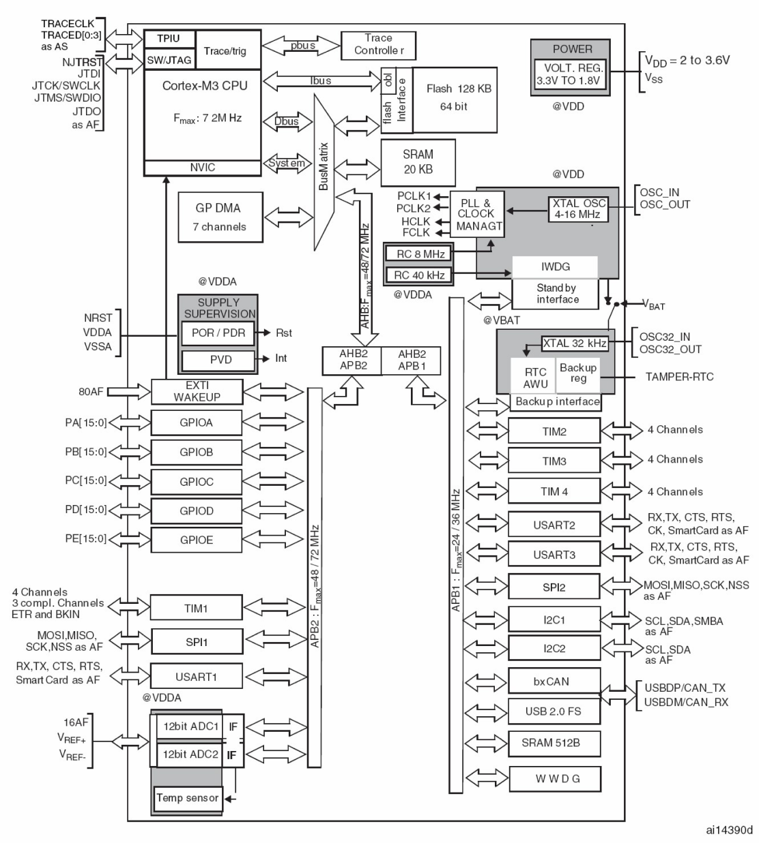

还是从这张图开始:

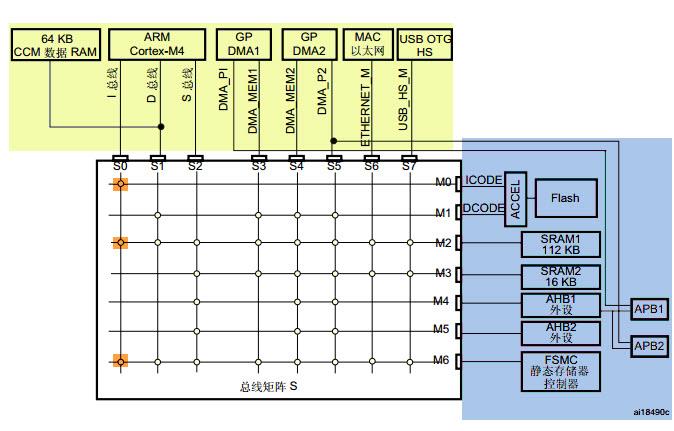

其中的Bus Matrix也就是总线矩阵可以调用循环调度算法从而实现总线仲裁的功能:

总线矩阵可实现以下部分互联:

- 八条主控总线:

- Cortex-M4 内核 I 总线,D 总线和 S 总线;

- DMA1 存储器总线,DMA2 存储器总线;

- DMA2 外设总线;

- 以太网DMA 纵向的;

- USB OTG HS DMA 总线;

- 七条被控总线:

- 内部FLASH ICode 总线;

- 内部FLASH DCode 总线;

- 主要内部SRAM1(112KB);

- 辅助内部SRAM2(16KB);

- AHB1 外设和AHB2 外设;

- FSMC 控制器

# 几条总控总线

I 总线:

也就是总线矩阵图中的 S0 端,此总线用于将 Cortex 内核的指令总线连接到总线矩阵

- 「内核通过此总线获取指令」

- 访问对象:包含代码的存储器

我们知道 STM32 有三种启动方式:从 FLASH 启动、从内部 SRAM 启动、从外部 RAM 启动,这三种存储器刚好对应的就是 M0、M2 和 M6 这三条总线

D 总线:

此总线用于将 Cortex 数据总线和 64KB CCM 数据 RAM 连接到总线矩阵

- 「内核通过此总线进行立即数加载和调试访问」

- 访问对象:代码或数据的存储器(内部FLASH 或通过FSMC 的外部存储器)

S 总线:

此总线用于将 Cortex 内核的系统总线连接到总线矩阵

- 「此总线用于访问位于外设或 SRAM 中的数据」也可通过此总线获取指令(效率低于 I 总 线)

- 访问的对象:112KB、16KB 的内部 SRAM、包括 APB 外设在内的 AHB1 外设、AHB2 外设以及通过 FSMC 的外部存储器

DMA 存储器总线:

此总线用于将DMA 存储器总线主接口连接到总线矩阵。 DMA 通过此总线来执行存储器数据的传入和传出

DMA 外设总线:

此总线用于将 DMA 外设主总线接口连接总线矩阵。DMA 通过此总线访问 AHB 外设或执行存储器之间的数据传输

以太网 DMA 总线:

此总线用于将以太网 DMA 主接口连接到总线矩阵。以太网DMA 通过此总线向存储器存取数据

USB OTG HS DMA 总线:

此总线用于将 USB OTG HS DMA 主接口连接到总线矩阵。USB OTG HS DMA 通过此总线向存储器加载/存储数据

# 什么是总线矩阵

总线矩阵的功能就是访问仲裁,「总线矩阵就像是一个裁判,由他来决定某个时刻允许谁与谁通信」

他的判断是有个方法的,叫做“轮换算法”,就是按顺序轮换,不能插队。一个时间只能有一个主动单元通过总线矩阵与一个被动单元连接。这里「主动单元是上述中 8 条主控总线,就是 CM4 内核和 DMA 控制器」,他们是控制端是有权限发出命令的主机。如果两个同时想要控制,就由总线矩阵判定当前给谁用;

7 条被控总线属于被动单元,比如 Flash、SRAM 就是用来存放数据的,相当于电脑硬盘和内存,完全是被动,任由 CPU 控制进行数据读写。

# 地址映射与位带操作

目前先简略的记一下,等到学到底层的时候再回来

# 地址映射

由于 STM32 是一个32位的单片机,所以做一个简单的计算:

所以在这

# 位带操作

关于位带操作可以参考这篇文章 (opens new window),写的非常好了

反正基本就是把一个外设的地址扩展为能控制详细功能的32倍的地址

# 时钟与复位

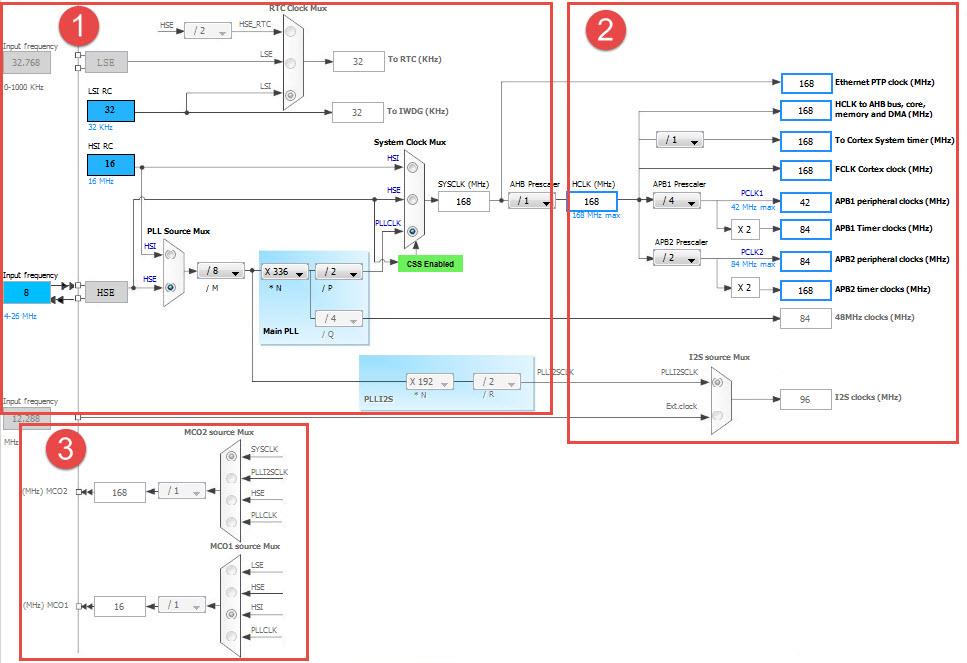

对于时钟树,CubeMX 中可以清晰地看到可以分为三个部分:第一部分是时钟的生成,第二部分是外设 时钟的配置,第三部分是主时钟输

# 时钟的生成

图中左边部分是时钟的生成功能选择,包括生成RTC(实时时间)时钟、 IWDG(独立看门狗)、FLITFCLK(闪存存储器接口)时钟、SYSCLK(系统时钟)。其中只有系统时钟是必须设置的,其他的都是与外设相关的,即有用到该外设才需要设置该时钟。

RTC 时钟可以从 3 个时钟来源,选择一种,为得到精准的实时时间我们一般需要使用 LSE(低速时钟),该时钟一般来源于芯片外接的 32.768KHz 的晶振。 独立看门狗只能使用芯片内的 32KHz 时钟源 LSI RC。

系统时钟是微控制器真正运行速度快慢的体现。STM32F407 芯片支持最大的系统时钟是 168MHz(支持长时间正常运行)。系统时钟也有 3 个可选来源:

- 第 1 种是直接使用芯片内部的16MHz 时钟源 HSI RC,显然直接使用这个很浪费资源,本来可以跑168MHz 的,现在拿来跑16MHz,所以这种一般都不会使用

- 第 2 种是直接把芯片外接的时钟源(一般是石英晶振)做为系统时钟,为得到 168MHz 的 系统时钟,我们需要外接 168MHz 的晶振,这个出于成本考虑,一般也不用

- 第 3 种是把外接时钟源或者芯片内部 8MHz 时钟源的 8 分频接入到 PLL(锁相环)倍频 得到PLLCLK,然后才得到系统时钟,实际应用中一般使用这种方法,只要外接一 个8 MHz 晶振就可以得到 168MHz 的系统时钟,另外一般选择外接 8MHz 的晶振 时钟源HSE 而不会选择内部的 HIS RC,一个是出于稳定性考虑,另 外8MHz 的晶振成本也不高。

# 外设时钟的配置

AHB 总线频率(HCLK)是通过 SYSCLK 分频得到的,最高支持 168MHz,所以一般选择 1 分频。I2S 外设是直接使用 HSE 分频一次后的时钟,ETH 是使用同 SYSCLK 时钟。APB1 和 APB2 总线的时钟都是由 HCLK 分频得到,其中 PCLK1(APB1 总线频率)最大只能是 84MHz,而 PCLK2(APB2 总线频率)可以达到 168MHz。从图 9-7 中 可以看到,挂在 APB1 总线上的外设有 TIM2~TIM7、TIM12~TIM14、USART2、USART3、 SPI2、SPI3、I2C1~3 等等,挂在 APB2 总线上的外设有SDIO、TIM1、TIM8、TIM9、 TIM11、USART1、USART6、ADC 等等。

# 主时钟的输出

STM32F40x 控制器有两个个主时钟输出引脚 MCO,第一个 MCO1 引脚(PA8) 有4个时钟源可以选择:HIS 时钟(内部高速时钟源)、LSE(外部低速时钟源)、 HSE(外部高速时钟源)、PLL 时钟

第二个 MCO2 引脚(PC9)有 4 个时钟源可 以选择:HSE 时钟、PLL 时钟、系统时钟(SYSCLK)、PLLI2S 时钟。MCO 输出时钟最高不能超过 100MHz,因为引脚最高频率不能超过100MHz